IBM 1620

|

|

The IBM 1620 was announced by IBM on October 21, 1959 and marketed as an inexpensive "scientific computer". It was withdrawn on November 19, 1970. Modified versions of the 1620 were used as the CPU of the IBM 1710 and IBM 1720 Industrial Process Control Systems.

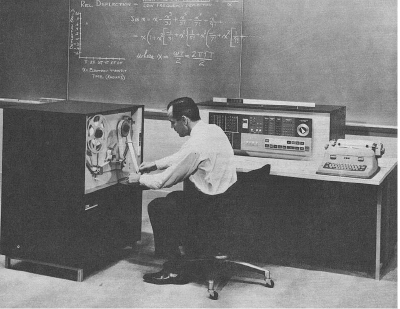

| Missing image IBM_1620_Model_1.jpg Image:IBM 1620 Model 1.jpg |

| IBM 1620 Model I Level G, running. |

| Contents |

The 1620's architecture

It was a variable "word" length decimal (BCD) computer with a memory that could hold anything from 20,000 to 60,000 decimal digits increasing in 20,000 decimal digit increments. While the 5-digit addresses could have addressed 100,000 decimal digits, no machine larger than 60,000 decimal digits was ever built.

Memory was accessed two decimal digits at the same time (even-odd digit pair for numeric data or one alphameric character for text data). Each decimal digit was 6 bits, composed of an odd parity Check bit, a Flag bit, and four BCD bits for the value of the digit in the following format:

C F 8 4 2 1

The Flag bit had several uses:

- In the least significant digit it was set to indicate a negative number (signed magnitude).

- It was set to mark the most significant digit of a number (wordmark).

- In the least significant digit of 5-digit addresses it was set for indirect addressing.

- In the middle 3 digits of 5-digit addresses (on the 1620 II) they were set to select one of 7 index registers.

In addition to the valid BCD digit values there were three special digit values (these could NOT be used in calculations):

C F 8 4 2 1

1 0 1 0 - Record Mark (right most end of record)

1 1 0 0 - Numeric Blank (blank for punched card output formatting)

1 1 1 1 - Group Mark (right most end of a group of records for disk I/O)

Instructions were fixed length (12 decimal digits), consisting of a 2-digit "op code", a 5-digit "P Address", and a 5-digit "Q Address".

Fixed-point data "words" could be any size from two decimal digits up to all of memory not used for other purposes.

Floating-point data "words" (using the hardware floating point option) could be any size from 4 decimal digits up to 102 decimal digits (2 digits for the exponent and 2 to 100 digits for the mantissa).

The machine had no programmer-accessible registers: all operations were memory to memory (including the index registers of the 1620 II).

Character and Op codes

The table below lists Alphameric mode Characters (and Op codes).

| BCD Character | Typewriter | Printer | Tape | Card | Core | MNEMONIC & Operation | Definition & Notes | ||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| In | Out | Out | In | Out | In | Out | Even | Odd | |||

| Blank | C | C | |||||||||

| invalid | Ж | 1 | FADD Floating Add | Optional special feature. | |||||||

| invalid | Ж | 2 | FSUB Floating Subtract | Optional special feature. | |||||||

| . | . | . | . | X0 8 21 | X0 8 21 | 12-3-8 12-1-2-8 | 12-3-8 | 21 | FMUL Floating Multiply | Optional special feature. | |

| ) | ) | ) | ) | X0C84 | X0C84 | 12-4-8 | 12-4-8 | 4 | |||

| invalid | Ж | 4 1 | FSL Floating Shift Left | Optional special feature. | |||||||

| invalid | Ж | 42 | TFL Transmit Floating | Optional special feature. | |||||||

| invalid | Ж | 421 | BTFL Branch and Transmit Floating | Optional special feature. | |||||||

| invalid | Ж | 8 | FSR Floating Shift Right | Optional special feature. | |||||||

| invalid | Ж | 8 1 | FDIV Floating Divide | Optional special feature. | |||||||

| + | + | + | + | X0C | X0C | 12 | 12 | 1 | |||

| invalid | Ж | 1 | 1 | AM Add Immediate | |||||||

| invalid | Ж | 1 | 2 | SM Subtract Immediate | |||||||

| $ | $ | $ | $ | X C8 21 | X C8 21 | 11-3-8 11-1-2-8 | 11-3-8 | 1 | 21 | MM Multiply Immediate | |

| * | * | * | * | X 84 | X 84 | 11-4-8 | 11-4-8 | 1 | 4 | CM Compare Immediate | |

| invalid | Ж | 1 | 4 1 | TDM Transmit Digit Immediate | |||||||

| invalid | Ж | 1 | 42 | TFM Transmit Field Immediate | |||||||

| invalid | Ж | 1 | 421 | BTM Branch and Transmit Immediate | |||||||

| invalid | Ж | 1 | 8 | LDM Load Dividend Immediate | Optional special feature (Model I). Standard (Model II). | ||||||

| invalid | Ж | 1 | 8 1 | DM Divide Immediate | Optional special feature (Model I). Standard (Model II). | ||||||

| - | - | - | - | X | X | 11 | 11 | 2 | |||

| / | / | / | / | 0C 1 | 0C 1 | 0-1 | 0-1 | 2 | 1 | A Add | |

| invalid | Ж | 2 | 2 | S Subtract | |||||||

| , | , | , | , | 0C8 21 | 0C8 21 | 0-3-8 0-1-2-8 | 0-3-8 | 2 | 21 | M Multiply | |

| ( | ( | ( | ( | 0 84 | 0 84 | 0-4-8 | 0-4-8 | 2 | 4 | C Compare | |

| invalid | Ж | 2 | 4 1 | TD Transmit Digit | |||||||

| invalid | Ж | 2 | 42 | TF Transmit Field | |||||||

| invalid | Ж | 2 | 421 | BT Branch and Transmit | |||||||

| invalid | Ж | 2 | 8 | LD Load Dividend | Optional special feature (Model I). Standard (Model II). | ||||||

| invalid | Ж | 2 | 8 1 | D Divide | Optional special feature (Model I). Standard (Model II). | ||||||

| invalid | Ж | 21 | TRNM Transmit Record No RM | (Model II) | |||||||

| invalid | Ж | 21 | 1 | TR Transmit Record | |||||||

| invalid | Ж | 21 | 2 | SF Set Flag | |||||||

| = | = | = | = | 8 21 | 8 21 | 3-8 1-2-8 | 3-8 | 21 | 21 | CF Clear Flag | |

| @ | @ | @ | @ | C84 | C84 | 4-8 | 4-8 | 21 | 4 | K Control (I/O device) | |

| invalid | Ж | 21 | 4 1 | DN Dump Numeric | |||||||

| invalid | Ж | 21 | 42 | RN Read Numeric | |||||||

| invalid | Ж | 21 | 421 | RA Read Alphameric | |||||||

| invalid | Ж | 21 | 8 | WN Write Numeric | |||||||

| invalid | Ж | 21 | 8 1 | WA Write Alphameric | |||||||

| A | A | A | A | X0 1 | X0 1 | 12-1 | 12-1 | 4 | 1 | NOP No Operation | |

| B | B | B | B | X0 2 | X0 2 | 12-2 | 12-2 | 4 | 2 | BB Branch Back | |

| C | C | C | C | X0C 21 | X0C 21 | 12-3 12-1-2 | 12-3 | 4 | 21 | BD Branch On Digit | |

| D | D | D | D | X0 4 | X0 4 | 12-4 | 12-4 | 4 | 4 | BNF Branch No Flag | |

| E | E | E | E | X0C 4 1 | X0C 4 1 | 12-5 12-1-4 | 12-5 | 4 | 4 1 | BNR Branch No Record Mark | |

| F | F | F | F | X0C 42 | X0C 42 | 12-6 12-2-4 | 12-6 | 4 | 42 | BI Branch Indicator | |

| UMK Unmask MK Mask | 1710 interrupt feature. Modifiers in Q field. | ||||||||||

| G | G | G | G | X0 421 | X0 421 | 12-7 12-1-2-4 | 12-7 | 4 | 421 | BNI Branch No Indicator | |

| BO Branch Out BOLD Branch Out and Load | 1710 interrupt feature. Modifiers in Q field. | ||||||||||

| H | H | H | H | X0 8 | X0 8 | 12-8 | 12-8 | 4 | 8 | H Halt | |

| I | I | I | I | X0C8 1 | X0C8 1 | 12-9 12-1-8 | 12-9 | 4 | 8 1 | B Branch | |

| -0 | N/A | - | - | N/A | X | 11-0 | 11-0 | 4 1 | |||

| J -1 | J | J | J | X C 1 | X C 1 | 11-1 | 11-1 | 4 1 | 1 | ||

| K -2 | K | K | K | X C 2 | X C 2 | 11-2 | 11-2 | 4 1 | 2 | ||

| L -3 | L | L | L | X 21 | X 21 | 11-3 11-1-2 | 11-3 | 4 1 | 21 | ||

| M -4 | M | M | M | X C 4 | X C 4 | 11-4 | 11-4 | 4 1 | 4 | ||

| N -5 | N | N | N | X 4 1 | X 4 1 | 11-5 11-1-4 | 11-5 | 4 1 | 4 1 | BNG Branch No Group Mark | Optional special feature. |

| O -6 | O | O | O | X 42 | X 42 | 11-6 11-2-4 | 11-6 | 4 1 | 42 | ||

| P -7 | P | P | P | X C 421 | X C 421 | 11-7 11-1-2-4 | 11-7 | 4 1 | 421 | ||

| Q -8 | Q | Q | Q | X C8 | X C8 | 11-8 | 11-8 | 4 1 | 8 | ||

| R -9 | R | R | R | X 8 1 | X 8 1 | 11-9 11-1-8 | 11-9 | 4 1 | 8 1 | ||

| invalid | Ж | 42 | BS Branch and Select | (Model II) | |||||||

| invalid | Ж | 42 | 1 | BX Branch and Modify Index Register | Optional special feature (Model II). | ||||||

| S | S | S | S | 0C 2 | 0C 2 | 0-2 | 0-2 | 42 | 2 | BXM Branch and Modify Index Register Immediate | Optional special feature (Model II). |

| T | T | T | T | 0 21 | 0 21 | 0-3 0-1-2 | 0-3 | 42 | 21 | BCX Branch Conditionally and Modify Index Register | Optional special feature (Model II). |

| U | U | U | U | 0C 4 | 0C 4 | 0-4 | 0-4 | 42 | 4 | BCXM Branch Conditionally and Modify Index Register Immediate | Optional special feature (Model II). |

| V | V | V | V | 0 4 1 | 0 4 1 | 0-5 0-1-4 | 0-5 | 42 | 4 1 | BLX Branch and Load Index Register | Optional special feature (Model II). |

| W | W | W | W | 0 42 | 0 42 | 0-6 0-2-4 | 0-6 | 42 | 42 | BLXM Branch and Load Index Register Immediate | Optional special feature (Model II). |

| X | X | X | X | 0C 421 | 0C 421 | 0-7 0-1-2-4 | 0-7 | 42 | 421 | BSX Branch and Store Index Register | Optional special feature (Model II). |

| Y | Y | Y | Y | 0C8 | 0C8 | 0-8 | 0-8 | 42 | 8 | ||

| Z | Z | Z | Z | 0 8 1 | 0 8 1 | 0-9 0-1-8 | 0-9 | 42 | 8 1 | ||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 12-0 | 0 | 421 | MA Move Address | Optional special feature (Model II). | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 421 | 1 | MF Move Flag | Optional special feature (Model I). Standard (Model II). |

| 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 421 | 2 | TNS Transmit Numeric Strip | Optional special feature (Model I). Standard (Model II). |

| 3 | 3 | 3 | 3 | C 21 | C 21 | 3 | 3 | 421 | 21 | TNF Transmit Numeric Fill | Optional special feature (Model I). Standard (Model II). |

| 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 421 | 4 | ||

| 5 | 5 | 5 | 5 | C 4 1 | C 4 1 | 5 | 5 | 421 | 4 1 | ||

| 6 | 6 | 6 | 6 | C 42 | C 42 | 6 | 6 | 421 | 42 | ||

| 7 | 7 | 7 | 7 | 421 | 421 | 7 | 7 | 421 | 421 | ||

| 8 | 8 | 8 | 8 | 8 | 8 | 8 | 8 | 421 | 8 | ||

| 9 | 9 | 9 | 9 | C8 1 | C8 1 | 9 | 9 | 421 | 8 1 | ||

| invalid | Ж | 8 | 4 | SA Select Address SACO Select Address, Contact Operate SAOS Select Analog Output Signal | 1710 feature. Modifiers in Q field | ||||||

| invalid | Ж | 8 | 42 | SLTA Select TAS SLAR Select ADC Register SLTC Select Real-Time Clock SLIC Select Input Channel SLCB Select Contact Block SLME Select Manual Entry | 1710 feature. Modifiers in Q field | ||||||

| invalid | Ж | 8 | F 42 | RNIC Read Numeric Input Channel | 1710 feature. Modifiers in Q field | ||||||

| invalid | Ж | 8 | F 421 | RAIC Read Alphameric Input Channel | 1710 feature. Modifiers in Q field | ||||||

| invalid | Ж | 8 | 8 | WNOC Write Numeric Output Channel | 1710 feature. Modifiers in Q field | ||||||

| invalid | Ж | 8 | 8 1 | WAOC Write Alphameric Output Channel | 1710 feature. Modifiers in Q field | ||||||

| invalid | Ж | 8 1 | BBT Branch on Bit | Optional special feature (Model II). | |||||||

| invalid | Ж | 8 1 | 1 | BMK Branch on Mask | Optional special feature (Model II). | ||||||

| invalid | Ж | 8 1 | 2 | ORF OR to Field | Optional special feature (Model II). | ||||||

| invalid | Ж | 8 1 | 21 | ANDF AND to Field | Optional special feature (Model II). | ||||||

| invalid | Ж | 8 1 | 4 | CPLF Complement Octal Field | Optional special feature (Model II). | ||||||

| invalid | Ж | 8 1 | 4 1 | EORF Exclusive OR to Field | Optional special feature (Model II). | ||||||

| invalid | Ж | 8 1 | 42 | OTD Octal to Decimal Conversion | Optional special feature (Model II). | ||||||

| invalid | Ж | 8 1 | 421 | DTO Decimal to Octal Conversion | Optional special feature (Model II). | ||||||

| RM | ‡ | (Stop) | (Stop) | 0 8 2 | E (Stop) | 0-2-8 | 0-2-8 | 8 2 | Record Mark | ||

| GM | | (Stop) | (Stop) | 0 8421 | E (Stop) | 0-7-8 | 1-2-4-8 | 8421 | Group Mark | ||

The table below lists Numeric mode Characters.

| Character | Typewriter | Printer | Tape | Card | Core | Definition & Notes | ||||

|---|---|---|---|---|---|---|---|---|---|---|

| In | Out | Out | Dump | In | Out | In | Out | |||

| Blank | 0 | 0 | 0 | C | 0 | 0 | C | |||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 12-0 12 | 0 | C | |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 12-1 | 1 | 1 | |

| 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 12-1 | 2 | 2 | |

| 3 | 3 | 3 | 3 | 3 | C 21 | C 21 | 3 12-3 1-2 12-1-2 | 3 | C 21 | |

| 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 12-4 | 4 | 4 | |

| 5 | 5 | 5 | 5 | 5 | C 4 1 | C 4 1 | 5 12-5 1-4 12-1-4 | 5 | C 4 1 | |

| 6 | 6 | 6 | 6 | 6 | C 42 | C 42 | 6 12-6 2-4 12-2-4 | 6 | C 42 | |

| 7 | 7 | 7 | 7 | 7 | 421 | 421 | 7 12-7 1-2-4 12-1-2-4 | 7 | 421 | |

| 8 | 8 | 8 | 8 | 8 | 8 | 8 | 8 12-8 | 8 | 8 | |

| 9 | 9 | 9 | 9 | 9 | C8 1 | C8 1 | 9 12-9 1-8 12-1-8 | 9 | C 8 1 | |

| -0 | _ 0 | _ 0 | - | - | X X0C | X | 11-0 | 11-0 | F | |

| -1 | _ 1 | _ 1 | J | J | X C 1 | X C 1 | 11-1 | 11-1 | CF 1 | |

| -2 | _ 2 | _ 2 | K | K | X C 2 | X C 2 | 11-2 | 11-2 | CF 2 | |

| -3 | _ 3 | _ 3 | L | L | X 21 | X 21 | 11-3 11-1-2 | 11-3 | F 21 | |

| -4 | _ 4 | _ 4 | M | M | X C 4 | X C 4 | 11-4 | 11-4 | CF 4 | |

| -5 | _ 5 | _ 5 | N | N | X 4 1 | X 4 1 | 11-5 11-1-4 | 11-5 | F 4 1 | |

| -6 | _ 6 | _ 6 | O | O | X 42 | X 42 | 11-6 11-2-4 | 11-6 | F 42 | |

| -7 | _ 7 | _ 7 | P | P | X C 421 | X C 421 | 11-7 11-1-2-4 | 11-7 | CF 421 | |

| -8 | _ 8 | _ 8 | Q | Q | X C8 | X C8 | 11-8 | 11-8 | CF8 | |

| -9 | _ 9 | _ 9 | R | R | X 8 1 | X 8 1 | 11-9 11-1-8 | 11-9 | F8 1 | |

| RM | ‡ | (Stop, WN) ‡ (DN) | (Stop) | ‡ | 0 8 2 | E (Stop, WN) 0 8 2 (DN) | 0-2-8 | 0-2-8 | C 8 2 | Record Mark On tape a WN punches EOL instead! |

| flag RM | _ ‡ | (Stop, WN) _ ‡ (DN) | (Stop) | W | X 8 2 | E (Stop, WN) X 8 2 (DN) | 11-2-8 12-2-8 | 11-2-8 | F8 2 | Flagged Record Mark On tape a WN punches EOL instead! |

| EOL | ‡ | (Stop, WN) ‡ (DN) | (Stop) | ‡ | E | E (WN) 0 8 2 (DN) | 0-2-8 | 0-2-8 | C 8 2 | End of line Tape only. Note: In memory is a Record Mark! |

| GM | | | (Stop) | G | 0 8421 | 0 8421 | 0-7-8 | 0-7-8 | C 8421 | Group Mark |

| flag GM | _ | _ | (Stop) | X | X 8421 | X 8421 | 12-7-8 | 12-7-8 | F8421 | Flagged Group Mark |

| NB | @ | @ | @ | C84 | C84 | 4-8 | C 84 | Numeric Blank | ||

| flag NB | _ @ | _ @ | * | X 84 | X 84 | 11-4-8 | F84 | Flagged Numeric Blank | ||

A flawed architecture

Although the IBM 1620's architecture was very popular in the scientific and engineering community, computer scientist Edsger Dijkstra pointed out several flaws in its design in EWD37, "A review of the IBM 1620 data processing system" (see http://www.cs.utexas.edu/users/EWD/index00xx.html at the Dijkstra archive at the University of Texas).

Dijkstra pointed out flaws including the fact that the 1620's Branch and Transmit instruction together with Branch Back allow a grand total of ONE level of nested subroutine call, forcing the programmer of any code with more than one level to decide where the use of this "feature" would be most effective. He also showed how the paper tape reading support of the 1620 could not properly read paper tapes with record marks on them, since record marks were used to terminate the characters read in storage (one effect of this, although he did not mention it, is that the 1620 cannot duplicate a tape with record marks: when punching a tape and the first record mark that was read in is encountered, the punch instruction punches an EOL on the tape instead and stops punching!).

These flaws (and similar ones in other machines) may have caused IBM's decline, which started in the 1960s, as a serious competitor in scientific computing, opening up a market which led to the development of the DEC PDP-8.

Hardware implementation

Most of the logic circuitry of the 1620 was a type of resistor-transistor logic (RTL) using "drift" transistors (a type of transistor invented by Herbert Kroemer in 1957) for their speed, that IBM referred to as SDTRL. Other IBM circuit types used were referred to as: Alloy (some logic, but mostly various non-logic functions, named for the kind of transistors used), CTRL (another type of RTL, but slower than SDTRL), CTDL (a type of diode-transistor logic (DTL)), and DL (another type of RTL, named for the kind of transistor used, "drift" transistors).

These circuits were constructed of individual discrete components mounted on single sided paper-epoxy printed circuit boards 2.5 by 4.5 inches (38 by 114 mm) with a 16 pin gold plated edge connector, that IBM referred to as SMS cards (Standard Modular System). The amount of logic on one card was similar to that in one 7400 series SSI or simpler MSI package (e.g., 3 to 5 logic gates or a couple of flip-flops).

These boards were inserted in sockets on racks, that IBM referred to as gates. The machine had the following "gates" in its basic configuration:

- "Gate A" - Forward hinged gate that swings out the back for access, after "Gate B".

- "Gate B" - Rear hinged gate that swings out the back for access.

- "Gate C" - Slides out back for access. Console Typewriter interface. Mostly relay logic.

- "Gate D" - Slides out back for access. Standard I/O interface.

There were two different types of core memory used in the 1620:

- Main memory

- Coincident Current X-Y Line addressing

- 20,000, 40,000, or 60,000 Digits

- 12 bit, even-odd Digit Pair

- 12 one bit planes in each module, 1 to 3 modules

- 10,000 cores per plane

- Coincident Current X-Y Line addressing

- Memory Address Register Storage (MARS) memory

- Word Line addressing

- 16 Words, minimum of 8 used in basic configuration

- Single Word read, multiple Word clear/write

- 24 bit, 5 Digit decimal Memory Address (no 8 - Ten Thousand bit stored)

- 1 plane

- 384 cores

- Word Line addressing

The address decoding logic of the Main memory also used two planes of 100 pulse transformer cores per module to generate the X-Y Line half-current pulses.

There were two models of the 1620, each having totally different hardware implementations:

Development history

In 1958 IBM assembled a team at the Poughkeepsie, New York development laboratory to study the "small scientific market". Initially the team consisted of Wayne Winger (Manager), Robert C. Jackson, and William H. Rhodes.

The competing computers in this market were the Librascope LGP-30 and the Bendix G-15, both were drum memory machines and it was concluded that IBM could offer nothing really new in that area. To compete effectively would require use of technologies that IBM had developed for larger computers, yet the machine would have to be produced at the least possible cost.

To meet this objective, the team set the following requirements:

- Core memory

- Restricted instruction set

- No divide or floating point instructions, use subroutines in the "general program package"

- Wherever possible replace hardware with existing logical machine functions

- No arithmetic circuits, use tables in core memory

- Least expensive Input/Output possible

- No punch cards, use paper tape

- No printer, use operators console typewriter

The internal code name CADET was selected for the machine. One of the developers says that this stood for "Computer with ADvanced Economic Technology", however others recall it as simply being one half of "SPACE - CADET", where SPACE was the internal code name of the IBM 1401 machine, also then under development.

The team expanded with the addition of Anne Deckman, Kelly B. Day, William Florac, and James Brenza. They completed the CADET prototype in the spring of 1959.

Meanwhile the San Jose, California facility was working on a proposal of its own. IBM could only build one of the two and the Poughkeepsie proposal won because "the San Jose version is top of the line and not expandable, while your proposal has all kinds of expansion capability - never offer a machine that cannot be expanded".

Management was not entirely convinced that core memory could be made to work in small machines, so Gerry Ottaway was loaned to the team to design a drum memory as a backup. During acceptance testing by the Product Test Lab repeated core memory failures were encountered and it looked likely that management's predictions would come true. However at the last minute it was found that the fan used to blow hot air through the core stack was malfunctioning, causing the core to pick up noise pulses and fail to read correctly. After the fan problem was fixed there were no further problems with the core memory and the drum memory design effort was discontinued as unnecessary.

|

| IBM 1620 Model I Level A (prototype), as it appeared in the IBM announcement of the machine. |

Following announcement of the IBM 1620 on October 22, 1959, due to an internal reorganization of IBM, it was decided to transfer the computer from the Data Processing Division at Poughkeepsie (large scale mainframe computers only) to the General Products Division at San Jose (small computers and support products only) for manufacturing.

Following transfer to San Jose, someone there jokingly suggested that the code name CADET actually stood for "Can't Add, Doesn't Even Try", referring to the use of addition tables in memory rather than dedicated addition circuitry. This stuck and became very well known among the user community.

Implementation "levels"

- Model I

- Level A; prototype.

- All flip-flops in the design were transistorized versions of the original Eccles-Jordan trigger circuit. While this machine was fully functional, it was found that the capacitor coupling used in these proved troublesome in the noisy signal environment of relays and timing cam driven switches used to drive the console typewriter. This necessitated a complete redesign of the machine to use S-R flip-flops instead (except for two triggers used to generate clocks for the S-R flip flops). However usage of the term Trigger was retained in all the documentation when referring to a flip flop.

- This is the only level using a one piece vertical control panel, when the design was transferred from Poughkeepsie to San Jose it was redesigned to the two piece angled control panel used on all production models.

- Level B; first production.

- This is the only level using a burnished aluminum lower control panel, later levels finished this panel with white.

- Level C; introduction of 1622 card reader/punch.

- Level D; introduction of 1311 disk drives.

- Level E

- Level F; introduction of Floating Point option.

- Level G; final version of the Model I

- Level A; prototype.

- Model II (no information on "Levels" available at this time)

- Model III

- Work was begun on a 1620 Model III in year-TBD, but the project was quickly canceled as IBM wanted to promote sales of their new System/360 and discontinue the old lines.

Patents

|

<p>

|

</table>